|

|

PDF GS1524A Data sheet ( Hoja de datos )

| Número de pieza | GS1524A | |

| Descripción | Adaptive Cable Equalizer | |

| Fabricantes | Gennum Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de GS1524A (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

GS1524A Adaptive Cable Equalizer

Features

• SMPTE 292M, SMPTE 344M and SMPTE 259M

compliant

• Automatic cable equalization

• Multi-standard operation from 143Mb/s to 1.485Gb/s

• Supports DVB-ASI at 270Mb/s

• Pb-free and RoHS Compliant

• Pin compatible with the GS9064 Cable Equalizer

• Manual bypass (useful for low data rates with slow

rise/fall times)

• Performance optimized for 270Mb/s and 1.485Gb/s

• Typical equalized length of Belden 1694A cable: 200m

at 1.485Gb/s, 350m at 270Mb/s

• 50Ω differential output (with internal 50Ω pull-ups)

• Manual output mute or programmable mute based on

max cable length adjust

• Cable length indicator for SMPTE 259M inputs

• Single 3.3V power supply operation

• Operating temperature range: 0°C to +70°C

Applications

• SMPTE 292M, SMPTE 344M and SMPTE 259M Coaxial

Cable Serial Digital Interfaces.

Description

The GS1524A is a second-generation high-speed BiCMOS

integrated circuit designed to equalize and restore signals

received over 75Ω co-axial cable.

The GS1524A is designed to support SMPTE 292M, SMPTE

344M and SMPTE 259M, and is optimized for performance

at 270Mb/s and 1.485Gb/s.

The GS1524A features DC restoration to compensate for

the DC content of SMPTE pathological test patterns. The

device also incorporates a Cable Length Indicator (CLI) that

provides an indication of the amount of cable being

equalized for data rates up to 360Mb/s.

A voltage programmable mute threshold (MCLADJ) is

included to allow muting of the GS1524A output when an

approximate selected cable length is reached for SMPTE

259M signals. This feature allows the GS1524A to

distinguish between low amplitude SD-SDI signals and

noise at the input of the device.

The bidirectional CD/MUTE pin indicates the presence of a

valid signal at the input of the GS1524A in addition to

functioning as a mute control input. The outputs of the

GS1524A will be forced to a mute state when an invalid

input reference signal is applied to the input of the device

or the application layer sets the CD/MUTE pin HIGH. If the

application layer forces CD/MUTE LOW, the serial digital

output of the device will always be active.

Power consumption is typically 265mW using a 3.3V

power supply.

The GS1524A is Pb-free, and the encapsulation compound

does not contain halogenated flame retardant (RoHS

Compliant).

GS1524A Adaptive Cable Equalizer

Data Sheet

28852 - 5

June 2009

www.gennum.com

1 of 16

1 page

1.2 GS1524A Pin Descriptions

Table 1-1: GS1524A Pin Descriptions

Pin Number

1

2, 15

3, 6, 11, 14

4, 5

7, 8

9

10

12, 13

16

Name

CLI

VCC

VEE

SDI, SDI

AGC+,

AGC-

BYPASS

MCLADJ

SDO, SDO

CD/MUTE

Timing

Type

Description

Analog

Analog

Analog

Analog

Analog

Not

Synchronous

Analog

Analog

Not

Synchronous

Output

Cable Length Indicator.

An analog voltage will be output proportional to the cable length

connected to the serial digital input.

NOTE: CLI is recommended for data rates up the 360Mb/s only.

Power

Most positive power supply connection.

Connect to +3.3V DC.

Power

Most negative power supply connection.

Connect to GND.

Input

Serial digital differential input.

– External AGC capacitor.

Connect pin 7 and pin 8 together through a 1uF capacitor.

Input

Forces the Equalizing and DC RESTORE stages into bypass mode

when HIGH. No equalization occurs in this mode.

Input

Maximum cable length adjust.

Adjusts the approximate maximum amount of cable to be equalized

(from 0m to the maximum cable length). The output is muted

(latched to the last state) when the maximum cable length is

achieved.

NOTE: MCLADJ is only recommended for data rates up to 360Mb/s.

Output

Equalized serial digital differential output.

Bidirectiona

l

STATUS SIGNAL OUTPUT / CONTROL SIGNAL INPUT

levels are LVCMOS/LVTTL compatible.

OUTPUT (CD):

Indicates the presence of a valid input signal. When the CD pin is

LOW, a valid input signal has been detected. When this pin is HIGH,

the input signal is invalid. If CD is set HIGH, the serial digital output

of the device will be forced to a steady state (latched to the last

state).

NOTE: This pin will indicate loss of carrier for data rates > 19Mb/s.

INPUT (MUTE):

When the MUTE pin is set HIGH by the application interface, the

serial digital output of the device will be forced to a steady state

(latched to the last state). When the MUTE pin is set LOW, the serial

digital output of the device will be active.

NOTE: The CD/MUTE pin is not functional when BYPASS is set HIGH.

GS1524A Adaptive Cable Equalizer

Data Sheet

28852 - 5

June 2009

5 of 16

5 Page

4.1 Serial Digital Inputs

The serial data signal may be connected to the input pins (SDI/SDI) in either a

differential or single ended configuration. AC coupling of the inputs is recommended, as

the SDI and SDI inputs are internally biased at approximately 1.8V.

4.2 Cable Equalization

The input signal passes through a variable gain equalizing stage whose frequency

response closely matches the inverse of the cable loss characteristic. In addition, the

variation of the frequency response with control voltage imitates the variation of the

inverse cable loss characteristic with cable length.

The edge energy of the equalized signal is monitored by a detector circuit which

produces an error signal corresponding to the difference between the desired edge

energy and the actual edge energy. This error signal is integrated by both an internal and

an external AGC filter capacitor providing a steady control voltage for the gain stage. As

the frequency response of the gain stage is automatically varied by the application of

negative feedback, the edge energy of the equalized signal is kept at a constant level

which is representative of the original edge energy at the transmitter. The equalized

signal is also DC restored, effectively restoring the logic threshold of the equalized signal

to its correct level independent of shifts due to AC coupling. The digital output signals

have a nominal voltage of 750mVpp differential, or 375mVpp single ended when

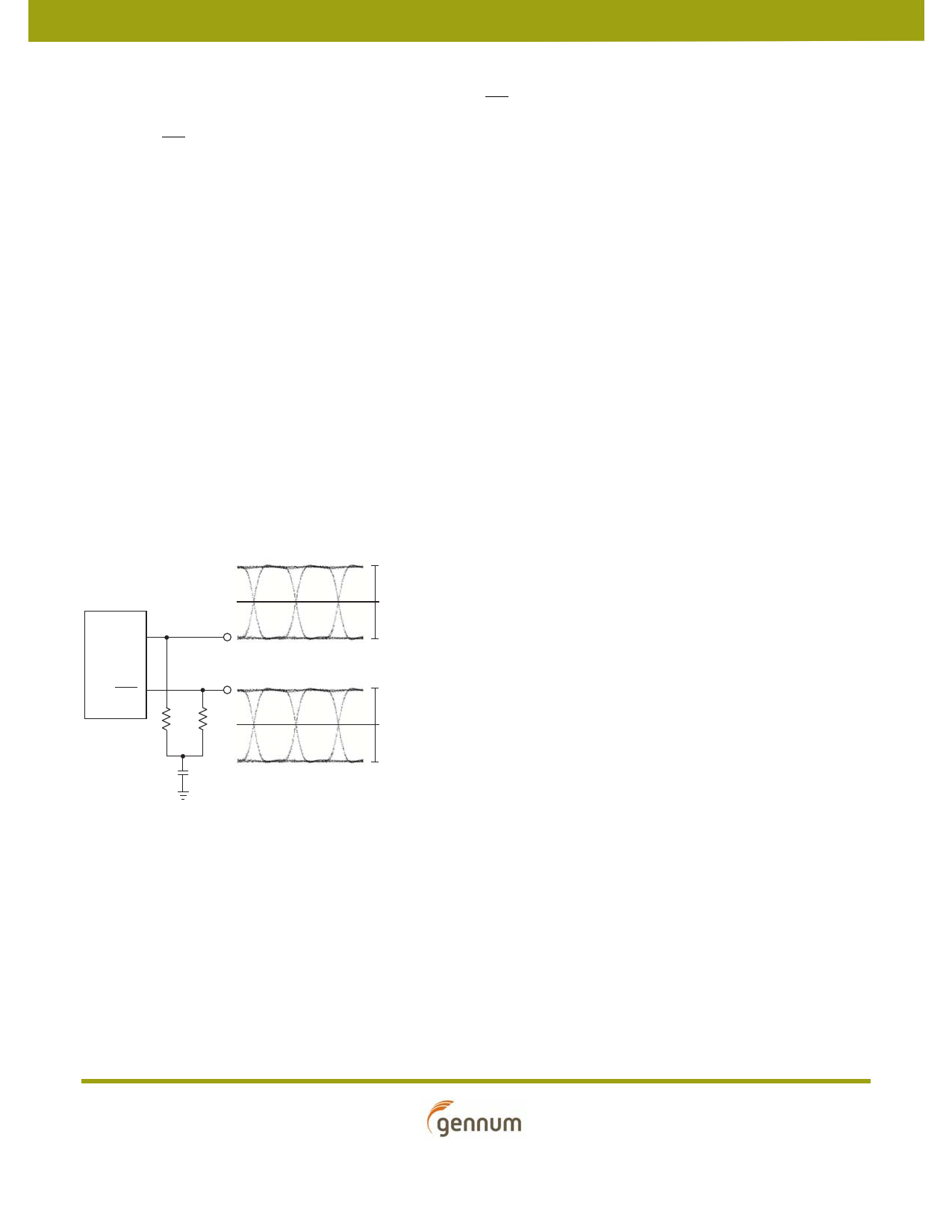

terminated with 50Ω as shown in Figure 4-1.

+187.5mV

SDO

VCM = 2.925V

typical

-187.5mV

SDO

50 50

+187.5mV

VCM = 2.925V

typical

-187.5mV

Figure 4-1: Typical Output Voltage Levels

4.3 Programmable Mute Output and Cable Length Indicator

For SMPTE 259M inputs, the GS1524A incorporates a programmable threshold output

mute (MCLADJ) and an analog cable length indicator (CLI).

GS1524A Adaptive Cable Equalizer

Data Sheet

28852 - 5

June 2009

11 of 16

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet GS1524A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GS1524 | HD-LINX-TM II Multi-Rate SDI Adaptive Cable Equalizer | Gennum Corporation |

| GS1524A | Adaptive Cable Equalizer | Gennum Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |